Project Scope & Motivation

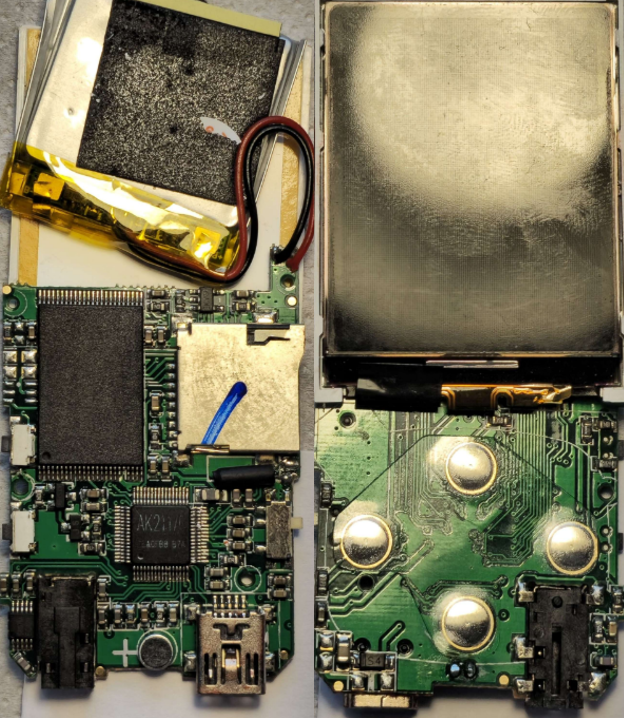

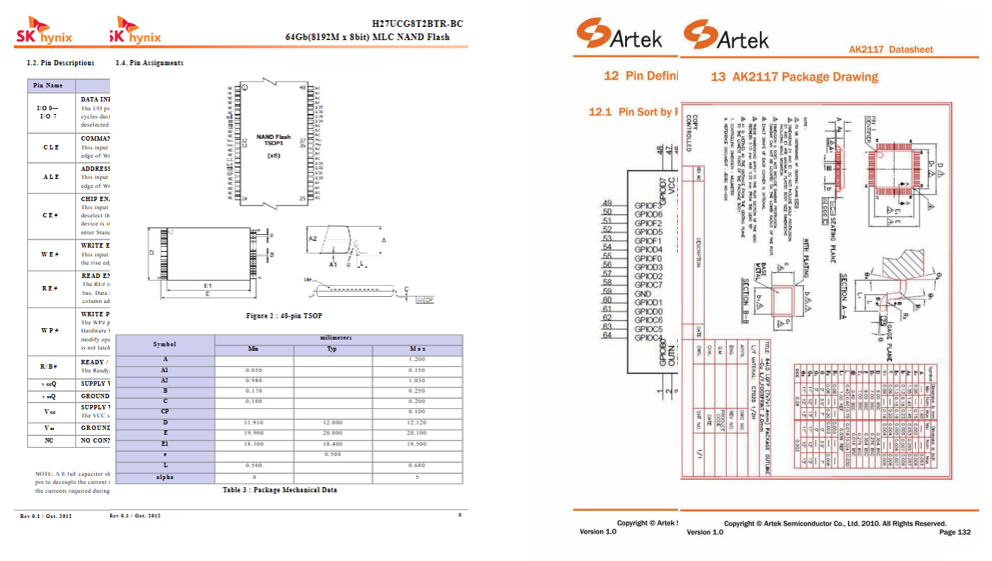

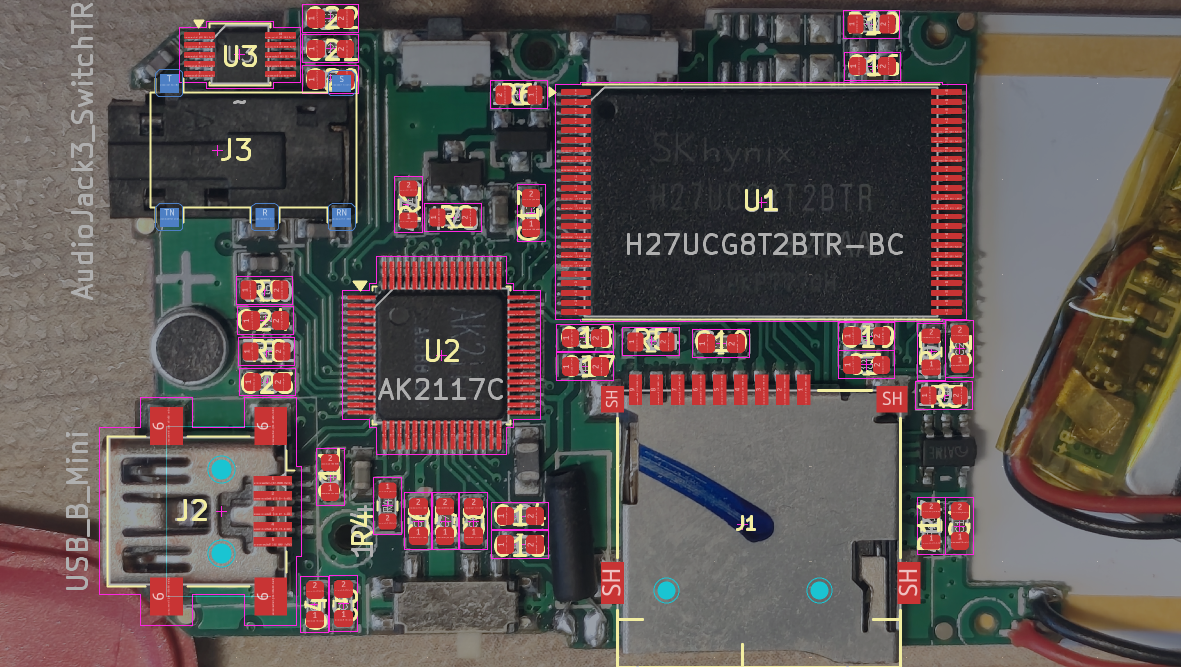

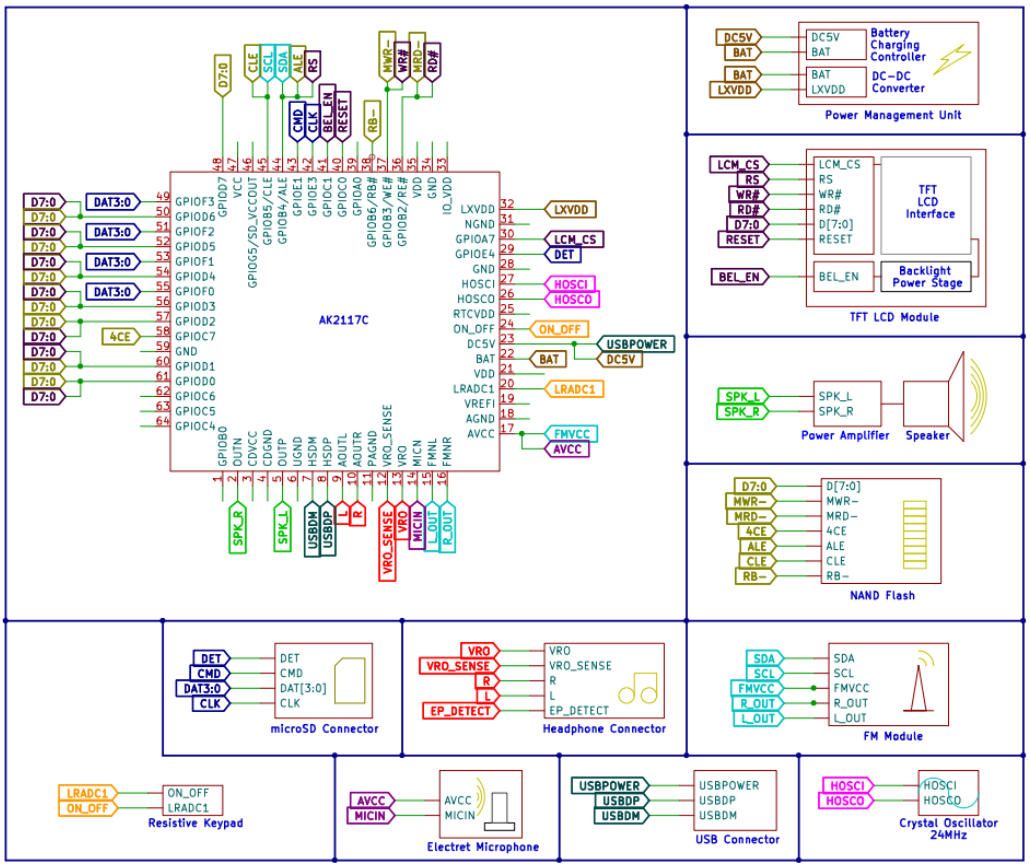

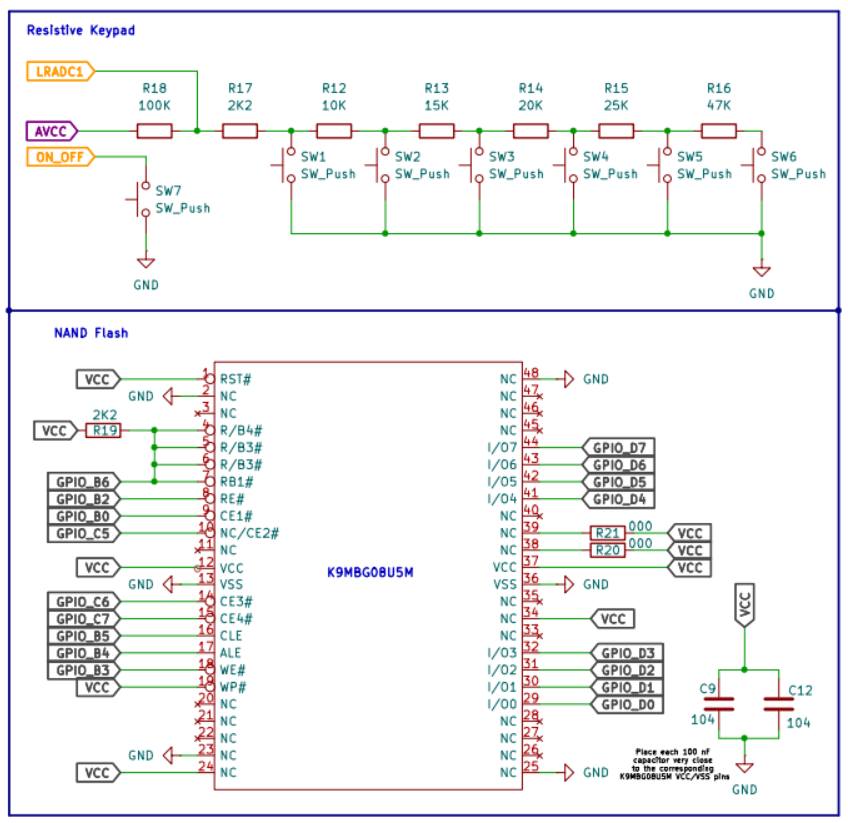

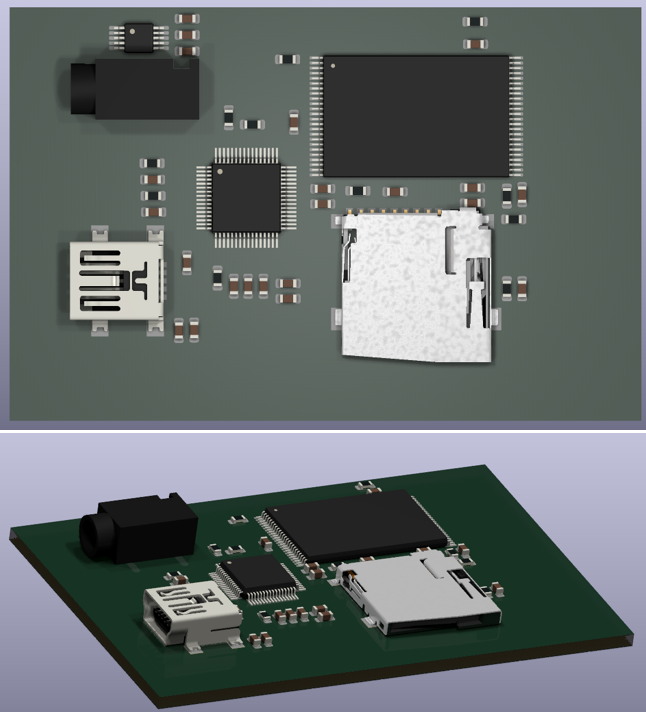

- Reverse engineer a consumer MP4 platform with scarce technical disclosure.

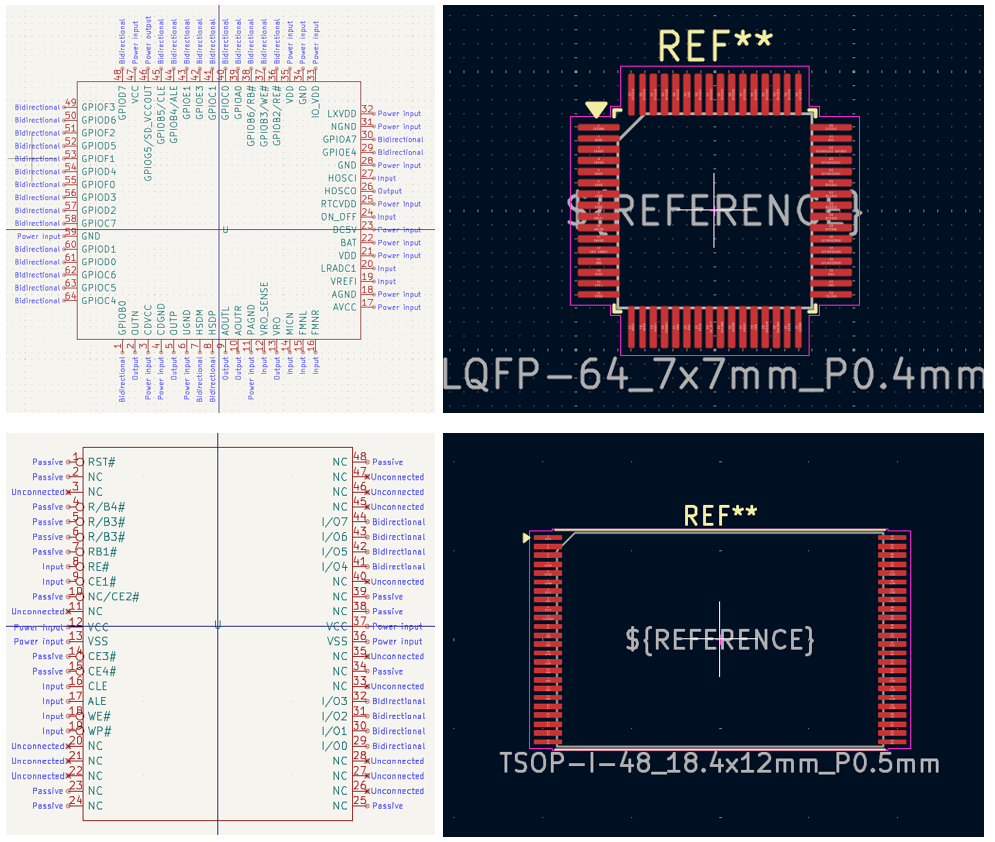

- Reconstruct architecture and design intent across power, clocks, storage, audio, and IO.

- Build an auditable technical baseline for subsequent schematic and simulation work.